[논리회로] 5 (2) S-R Flip-Flop 과 J-K Flip-Flop

5.5 Clock signals and clocked Flip-Flops

디지털 시스템은 동기적 or 비동기적으로 동작 가능

동기적 - 출력을 특정 시간에만 ! clock과 동기화되어 바뀔 수 있음

비동기적 - 출력은 입력이 바뀌면 언제든지 상태가 변할 수 있음 ( set, reset 이 입→출력에 영향을 줌)

Clock 신호 - 직사각형 pulse train

PGT : clock pulse 가 0 → 1 positive edge/transition

NGT : clock pulse 가 1 → 0 negative edge/transtition

Clock flip-flop (ff) 메모리 소자이며," clock 입력에 transition 이 일어났을 때" 제어입력 control inputs 에 따라 상태가 바뀜

→ edge - triggered

제어입력은 출력이 "어떤 값으로 변할지 결정하고, clk는 "언제" 출력이 변할지 결정 !

Setup time (tS) : CLK treansition 이전에 제어입력을 적절한 레벨로 유지해야 하는 최소 시간

Hold time(tH) : CLK transition 이후에 제어입력을 적절한 레벨로 유지해야 하는 최소 시간

5.6 S-R Flip-Flop

- S R 입력은 동기적 input

- edge detector → enable 로서 동작 → NAND latch

- CLK* 은 CLK/CLK' 보다 크기가 작다. 크기가 작아야 다음 상태나 변화하는 순간을 정확하게 포착할 수 있기 때문이다. CLK* 의 역할은 변화를 감지하는 데에 사용되는 것이기 때문에 !!

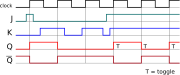

5.7 J-K Flip-Flop

- SR FF 처럼 동작함 + J는 SET K는 RESET/CLEAR

- 하지만 J, K = 1 이 모호한 출력을 갖지 않고, 이전 출력값을 toggle 해서 출력한다.

- SR FF 기능 + toggle 기능

- T FF : J=1, K=1인 FF

- 이때, 회로도를 살펴보면 , 출력값이 다시 pulse steering circuit 의 입력으로 들어가는 구조, 즉 피드백 구조이다(이전 상태를 기억함)