7.1 Asynchronous (=ripple) counters

clock와 동기화되어 변경되지 않아 구현이 간단하다.

Mod 2^N Counter

: n개의 FF 를 이용하면 mod counter를 만들 수 있다.

- 비동기적 카운터이기 때문에 Clock과 동기화되어 변경되지 않음

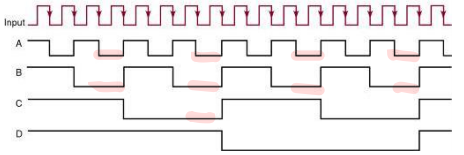

7.2 ripple counter

각 비트가 앞 비트의 출력에 의존하는 방식으로 작동한다. 즉, 한 비트의 상태 변화가 다음 비트로 전파되는 방식이다.

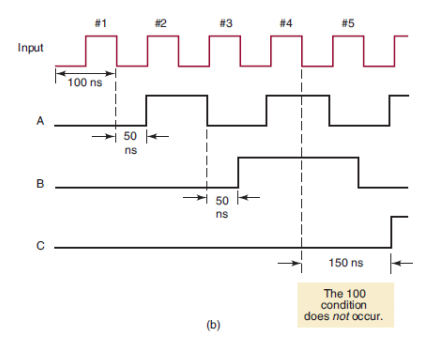

각각의 플립플롭은 고유의 전파지연시간 (tpd) 가 있어서 출력 펄스가 인가되더라도 출력이 바로 나오지 않고 tpd만큼의 시간이 경과된 이후에 나오게 된다.

Q. ripple counter 가 제대로 작동하지 않는 경우는 ?

전파지연시간이 클럭주기에 비해 매우 작으면 2진카운터로 사용하기에 별 문제는 없다. 하지만 입력 클럭 펄스의 주파수가 매우 높아지면 상황은 달라진다.

1. counter의 비트길이가 커지면 누적이 쌓인다.

각 비트가 변화하는 데에는 시간이 걸리는데, 비트가 많을수록 이러한 propagation delay가 누적된다. 전파지연이 여러 비트에 걸쳐 누적되면 전체 카운팅 속도가 느려지고, 정확한 카운팅이 이루어지지 않을수 있는 것이다.

2. clock의 주기가 매우 짧은 경우

리플 카운터에서 클록 신호는 각 플립플롭에 순차적으로 전달되며, 각 플립플롭의 출력이 다음 플립플롭의 입력으로 사용되는 구조이다. 이때 클록 주기가 너무 짧으면, 각 플립플롭이 변화할 시간을 충분히 가지지 못하고, 이로 인해 출력이 제대로 반영되지 않거나 정확하지 않게 될 수 있다.

누적된 propagation delay 는 ripple counter 동작에 큰 오류를 미칠 수 있다!!

해결방법 !

- 입력 펄스 사이의 주기를 counter의 총 propagation delay 보다 길게 설정하면 된다.

정상적인 동작 조건 : Tclock >= n * tpd

최대 주파수 : fmax = 1/(n*tpd)

→ 비동기식 카운터는 매우 높은 주파수에는 적절치 않으며, 특히 많은 비트 수를 갖는 카운터에는 사용이 어렵다.

짧은 시간 동안 원하는 출력값이 전달되지 않는 순간적인 상태를 보기에 사람의 눈은 너무 느리지만,, 전자회로는 이를 감지할 만큼 충분히 빠르다. 이러한 순간적인 펄스를 글리치라고 한다. 글리치로 인해 비동기식 카운터는 설계는 간단하나, 디지털 응용에서 매우 제한적으로 사용된다.

Q. 카운터에 플립플롭이 추가됨에 따라 리플 카운터의 최대 주파수 한계가 감소하는 이유를 설명하라 .

플립플롭이 추가됨에 따라 전파지연이 누적되어 카운터의 전체 주기가 길어지고, 이로 인해 카운터가 동작할 수 있는 최대 주파수는 점차 낮아진다.

Q. 어떤 JK FF의 전파지연 tpd는 12ns이다. 이 ff가 10MHZ까지 동작할 때 가장 크게 사용할 수 있는 MOD수는?

전파지연 tpd = 12ns

카운터의 최대 동작 주파수 fmax = 10MHz

1. 주기를 구하려면, 주파수의 역수로 계산할 수 있다.

f = 10MHz = 10,000,000Hz

T = 1/10000000 = 100ns

2. 카운터 주기와 전파지연

100ns >= n * 12

8.33>= n

n은 최대 8개 (n은 플립플롭의 수)

→ MOD-256

cf) 10ns = 100MHz

지금까지 리플 카운터(비동기식 카운터)의 경우 플립플롭의 전파 지연이 누적된다는 문제가 있었다. 이러한 문제점은 모든 플립플롭이 입력 클럭 펄스에 의해 동시에 기동되는 동기식/병렬 카운터를 통해 해결할 수 있다.

모든 플립플롭에 입력 펄스가 인가되기 때문에 각 플립플롭이 입력 클럭 펄스에 의해 반전되거나 현 상태를 유지할 수 있도록 하는 회로가 추가되어야 한다.(따라서 리플 카운터보다 더 많은 회로 소자가 필요하다. )

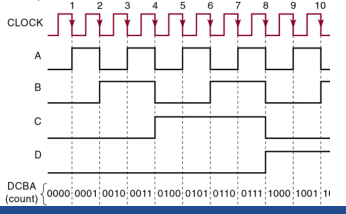

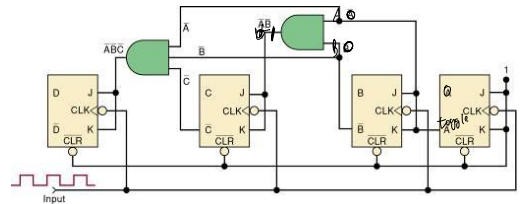

7.3 Synchronous counter

: 모든 FF는 CLK 에 동기화하여 동시에 trigger 된다.

- 하위단의 FF출력이 모두 1일 때 그 FF의 J-K 입력이 1이 되도록 설계한다.

→ 임의의 플립플롭에 대해 하위 단의 플립플롭 출력이 모두 HIGH일 때에만 그 플립플롭의 J와 K입력이 HIGH 상태가 되도록 연결되어야 한다.

- 아래 회로의 경우 클럽 입력의 하강 천이 때 항상 반전될 수 있도록 J , K 입력은 항상 HIGH가 되어야 한다.

모든 플립플롭은 입력 클럭 펄스의 하강천이에 모두 동기되어 있기에 비동기식 카운터와 달리 플립플롭의 전파 지연 시간으로 인한 문제가 발생하지 않는다.

Asynchronise VS Synchronise

비둥기식 카운터의 총 지연시간 = tpd + and게이트의 tpd (카운터 내의 플립플롭 수에 영향을 받지 않고, 같은 수의 플립플롭을 갖는 비동기식 카운터 경우보다 훨씬 짧다! )

→ 동기식 카운터는 훨씬 높은 입력 주파수를 사용하는 곳에서도 사용 가능하다.

주어진 170 ns\frac{1}{70 \, \text{ns}}를 MHz로 변환하는 방법을 설명하겠습니다.

나노초(ns)에서 헤르츠(Hz)로 변환

먼저, 주어진 값 170 ns\frac{1}{70 \, \text{ns}}는 주기를 나타내는 값입니다. 이 값을 주파수(Hz)로 변환하려면 주기의 역수를 취해야 합니다.

1 나노초는 1 ns=10−9 s1 \, \text{ns} = 10^{-9} \, \text{s}이므로, 70ns는 70×10−9 s70 \times 10^{-9} \, \text{s}입니다.

주파수는 주기의 역수입니다:

f=1Tf = \frac{1}{T}

여기서 TT는 주기입니다.

따라서,

f=170×10−9 s=170×109 Hz=14.2857×106 Hzf = \frac{1}{70 \times 10^{-9} \, \text{s}} = \frac{1}{70} \times 10^9 \, \text{Hz} = 14.2857 \times 10^6 \, \text{Hz}

즉,

f=14.2857 MHzf = 14.2857 \, \text{MHz}

결론

170 ns\frac{1}{70 \, \text{ns}}는 약 14.29 MHz입니다.

Q. MOD-64 병렬 카운터를 구성하기 위해서는 몇 개의 논리소자가 필요한가?

6개의 FF 4개의 AND 게이트

Q. 위 문제에서 MSB 플립플롭의 J,K 입력을 구동하기 위한 논리신호는 무엇인가?

ABCDE

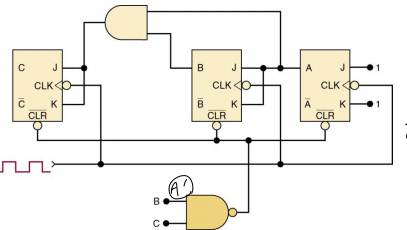

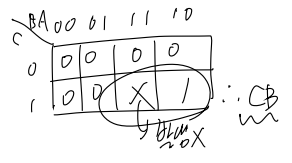

7.4 Counters with MOD number < 2^n

기본 동기식 카운터는 n개의 FF가 있으면 2^N 개까지 셀 수 있다.

더 작은 숫자를 세려면 중간 숫자 몇 개 건너뛰게 만들자 ex) mod-6을 구현하려면 mod-8에서 6과 7을 건너뛰는 방식

- 최소 n(ff개수)를 찾아 mod-n 을 설계하고, 원하는 특정 mod값일 때 nand로 모든 ff에 Asynchronise CLEAR 입력을 인가한다.

글리치 신호 문제의 발생

B에서는 출력신호가 110의 상태에서 클리어 되기 전 순간적으로 일어나는 스파이크/글리치 신호가 포함되어 있다. 이러한 글리치는 펄스폭이 매우 좁아 신호 LED나 숫자 표시장치에 나타나지는 않는다. 그러나 출력 B가 카운터의 외부 회로를 구동하는 데 이용된다면 문제가 될 수 있다 !!

- mod-N에서 MSB의 주파수는 회로 전체의 특성을 반영하게 된다.

→ 동기화된 디지털 회로를 설계할 때 , FF 출력이 다른 FF의 CLK나 asynchronise PRE/CLR 의 입력으로 넣으면 위험하다!

7-5 Synchronous Down and UP/Down Counters

- UP counter와 달리 상위 플립플롭의 J,K입력을 제어하는 데 플립플롭의 반전된 풀력을 사용한다는 점이 다르다.

- 숫자를 역순으로 세려면, 하위단의 FF 출력이 모두 0일 때 J-K 입력이 1이 되도록 설계한다.

Synchronous Down and up/down counters ( 1일 때 up, 0일 때 inverse값 선택되어 down)

7-6 Presettable Counters

- 카운터를 원하는 숫자에서 시작할 수 있다.

- 카운터의 병렬 로딩이라고도 한다.

...

'Major S-T-U-D-Y > Digital System' 카테고리의 다른 글

| [논리회로] 7 (2) 동기식 J/K , D FF 카운터의 설계과정 (0) | 2024.12.01 |

|---|---|

| [논리회로] 5 (2) S-R Flip-Flop 과 J-K Flip-Flop (0) | 2024.11.17 |

| [논리회로] 5 (1) NAND/NOR Gate Lanch (set/reset) (0) | 2024.11.17 |

| [논리회로] 8 (2) 벨로그_if-else와 case 문 (0) | 2024.11.17 |

| [논리회로] 8 (1) 벨로그 기초 문법과 테스트벤치 (1) | 2024.11.17 |